Overview

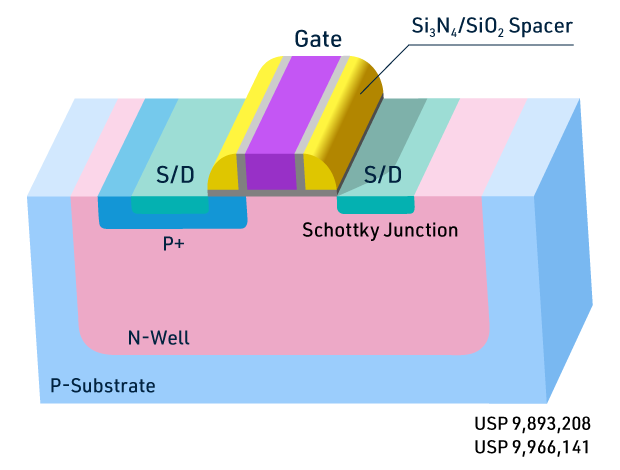

NSCore’s TwinBit™ Gen-2 supports 40nm to 22nm process nodes and beyond. As well as the Gen-1, TwinBit™ Gen-2 does not require any additional masks or process steps. Utilizing newly developed “Pch Schottky Non-Volatile Memory Cell”, it achieves ultra-low-power operations.

Pch Schottky NVM Cell

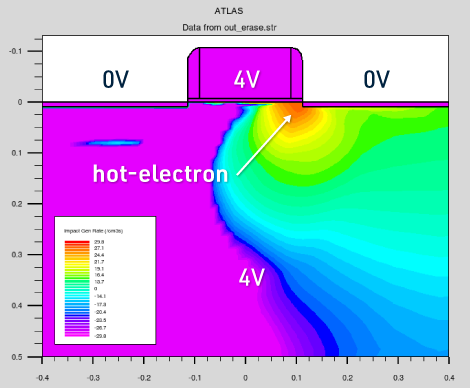

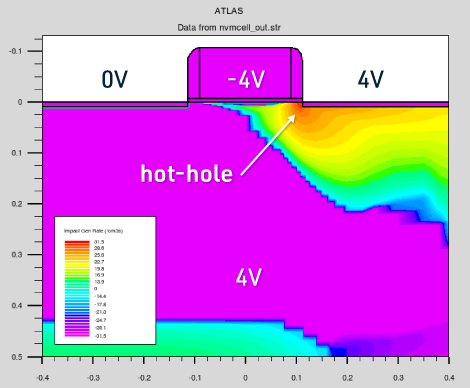

T-CAD Simulation

for Program / Erase

Hot carrier injection can be controlled by cell bias

-

Hot-Hole Generation Distribution in Program

-

Hot-Electron Generation Distribution in Erase